## Inevitability of Micro-Packages Replacing Large Modules for High Power GaN & SiC Products Courtney R. Furnival January 30, 2017

The power Wide Band Gap (WBG) market is ramping with SiC and GaN devices replacing Si FETs and IGBTs for higher power and higher voltage products. These WBG materials will not only provide far superior performance and speed, but with higher power densities, efficiency, reliability and cost effectiveness. Certainly conversion from Si to these WBG materials has been complex, as WBG device processing, types and configurations are optimized. The progress has been slow but steady, and we are finding that different application circuits are needed to optimize products for WBG devices.

The writing has been on the wall for traditional high power leaded packages and modules. If we read the fine print on the wall, we see it is inevitable that large high power packages and modules must be replaced by leadless micro-packages, and that system integration and architecture are essential to enabling the WBG improvements in performance, speed, power density, efficiency and reliability. Today's power packages and modules are not only unsuitable for WBG devices; they are already limiting performance of today's power Si FET and IGBT devices. It will take a market leading early adopter company to provide lasting change impact in the industry.

The power package and module industries have a lot of momentum, and the GaN and SiC industries focus has been on device development. As a result current WBG device potential performance, efficiency and power density have not been realizable in real applications. It is now time to turn our attention to optimum packaging power for GaN and SiC devices. The good thing is that suitable leadless, wire bondless and surface mount technologies already exist for the required WBG packaging, and it is time to hijack these package technologies for power package architectures, and move forward with higher power WBG devices.

Early WBG SMD packages included QFN and LGA types with some performance improvements, and new Power QFN and Embedded LGA increase performance further, but at the expense of increased manufacturing complexity, costs and interface reliability.

A more compelling option is demonstrated in the "µMaxPak" as described in U. S. patent 9214416. This new package architecture provides double sided assembly of QFN type leadframes and LGA type substrates, by incorporation open bottom-side cavity(s) for WBG power die, thereby enabling more components to be included, optimum electrical and thermal performance, power density, and reliability.

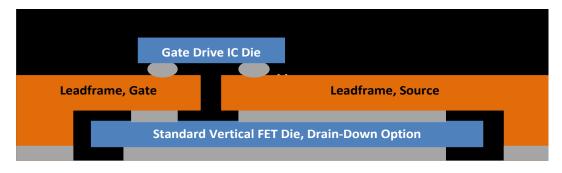

Figure 1: µMaxPak Smart Single-Switch Cross-Section-

Figure 1 shows the basic  $\mu$ MaxPak Single-switch architecture with WBG power die in bottom-side cavity with exposed drain pad, and top-side gate-driver IC with driver output pads directly over the WBG gate and source leadframe pad. The integrate gate driver die virtually eliminates common-source inductance and enables highest switching speed.

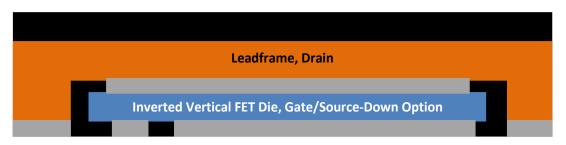

Figure 2: µMaxPak Inverted Single-Switch Cross-Section-

Figure 2 shows inverted  $\mu$ MaxPak architecture with WBG gate and source pads exposed on the bottom-side. The leadless and wirebondless  $\mu$ MaxPak with heavy copper leadframe provides very low current loop inductance (L) and resistance (R) for interconnect current loop. Parasitic L and R are reduced further with half-bridge (HB) packaging, micro-packaged) hi-side and lo-side die. See Table 1 for summary of achievable  $\mu$ MaxPak performance based on a 5x5mm to 5x6mm die.

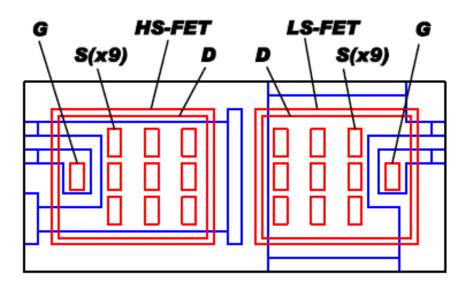

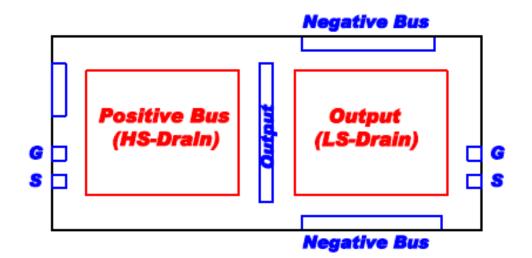

Figures 3a and 3b show HB  $\mu$ MaxPak leadframe layout with 5mmx6mm power SiC die, and the 8mm x15mm  $\mu$ MaxPak Half-bridge package for 125A/1200V demonstrate exceptionally low current loop-inductance(0.1-0.2nH) and loop-resistance(100-200 $\mu$ ohm) shown in Table 1 . Adding integrated gate-driver IC can virtually eliminate any common-mode gate inductance. The Rjc for each die can be <0.1C/W, accommodating higher power and higher efficiency. The same HB package can accommodate two 5mmx6mm 650V GaN Die with 650V/250A output.

| Parameter                           | Value   | Units |

|-------------------------------------|---------|-------|

| Switching Frequency @ 100 A         | >100    | MHz   |

| Loop Inductance                     | 0.1-0.2 | nH    |

| Loop Resistance                     | 100-200 | μohms |

| Common-Mode Inductance              | 0.0     | nH    |

| Thermal Resistance, T <sub>jc</sub> | 0.1     | °C/W  |

Table 1: Potential µMaxPak HB Performance with 5x5 mm WBG Die

Figure 3a: 15mmx8mmµMaxPak 1200 V/125A SiC FET HB, Top X-ray View

Figure 3b: 15mmx8mm µMaxPak 1200V/125A SiC FET HB, Bottom View

Furthermore, the  $\mu$ MaxPak technology enables minimum development time, cost and risk, based on proven low cost commercial assembly existing QFN and LGA technologies.

System integration and performance are equally enhanced with high-density leadless  $\mu$ MaxPak power packages. The compact systems further enable high speed GaN and SiC power device performance, by eliminating long electrical connectors, leads, and terminals, which increase size and cost of convention module type building blocks used with IGBT products at hundreds of volts and hundreds of amperes. The integrated systems reduce the larger required isolation spacing by eliminating many exposed high voltage leads and terminals. SMD board spacing can generally comply to UL pollution degree 1 with suitable SMD under-fills and coatings, whereas exposed leads and terminal spacing typically require pollution degree 2 or 3 spacing. These minimum spacings are very small relative to traditional exposed lead and terminal spacing, but traditional product already use these spacings inside industrial and commercial hi-power modules with suitable coating materials.

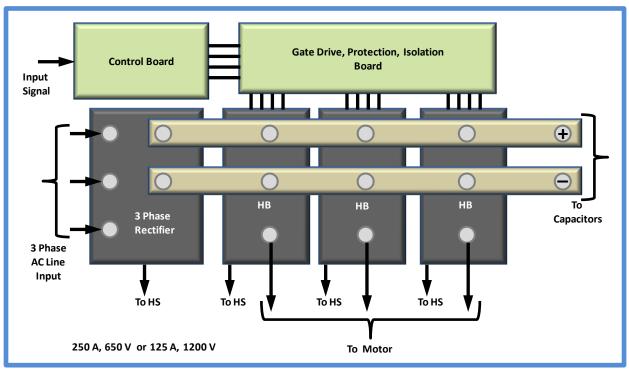

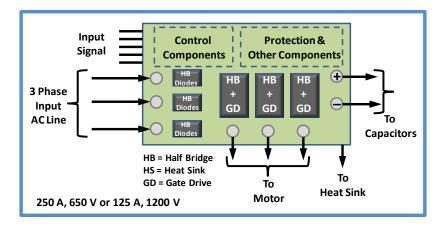

Figure 4a shows traditional 600/1200V Si Motor Drive building block architecture with traditional HB IGBT modules, and Figure 4b shows 600V GaN/1200V SiC  $\mu$ MaxPak Power Components an all SMD Motor Drive Thermal Mother-Board architecture with power GaN SiC/GaN switches in  $\mu$ MaxPak HB packages with integrated gate driver ICs. The example shows enhanced Mode GaN die and MOSFET SiC die, but other GaN and SiC type die can be used with modified leadframes. It should be noted that regardless of WBG device type, die and leadframe pads should be co-designed for optimum performance, manufacturability and reliability.

Figure 4a: Traditional Si IGBT Motor Drive Architecture

Figure 4b: Inevitable All-SMD WBG Motor Drive Power PCB Architecture

Power WBG devices like GaN & SiC are very small with high power density, speed, performance and efficiency. The reduced parasitics of the very small devices are an integral part of these improvements. But, product performance is limited by the combined parasitics of device, package and system. If package and system size and parasitics are not reduced accordingly, much of the WBG device advantages will not be realized in finished products. At lower powers and voltages, some bump-chip GaN devices have eliminated package parasitics by eliminating the package, but at higher power and voltages packages are required for environmental protection, high-voltage isolation, high-current inter-connects and power dissipation. Even some bump-chip or packageless devices require added complexity increasing parasitics on their system PCB.

SMD packages can reduce loop L and R by eliminating leads, terminals and wire bonds. Importantly, smaller packages can reduce system size, inter-connect length and associated loop L and R. Equally important, SMD system assembly eliminates complex, costly and large leads, terminals, connectors, hardware, and associated minimum separation required for the highvoltage isolation.

Now consider that SMD system assemblies are easier, cheaper and potentially more reliable. New power SMD packages like the  $\mu$ MaxPak are different, but built on proven commercial QFN and LGA technologies, which are available and require less tooling, NRE and development time. Such packages accommodate integration of gate drives and other components, further enhancing device performance and providing better control of parasitics by the device manufacturer.

So existing WBG packages are severely limiting product performance, and power micro-SMD packages are inevitable for power WBG devices to evolve to their real potential.